HD Camera Image Signal Processor

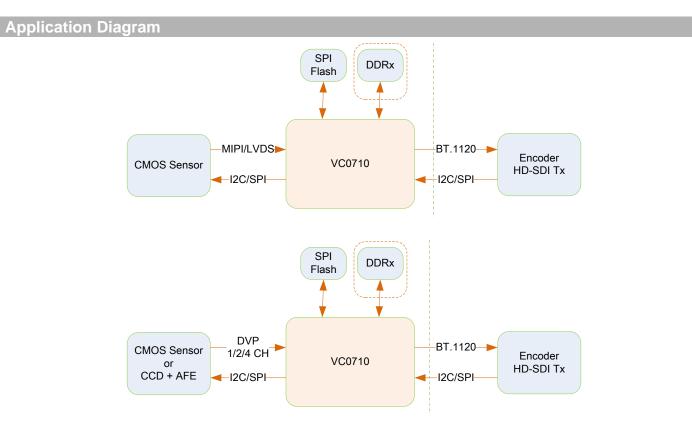

**VC7103** is a dedicated ISP chip for surveillance HD cameras. Through the serial (the MIPI/LVDS) or parallel (DVP, CCIR656/BT.1120) interface, it accepts data from CMOS or CCD sensor, then outputs processed high quality YUV data through DVP or CCIR656/BT.1120 interface. Besides the basic ISP function, VC0710 also supports Electronic Image Stabilization (EIS), Wide Dynamic Range (WDR), 3D NR (3D noise reduction) and other advanced image preprocessing functions.

# **KEY FEATURES**

#### **Video Input Interface**

4 channels 12bits, or 1 channel 16bits DVP parallel input interface Support MIPI up to 4 data lanes Support LVDS/SubLVDS up to 12 data lanes Support CCIR656/BT.1120 input interface

### Video Output Interface

Support 1 channel 20bits DVP parallel output Support CCIR656/BT.1120 output interface

#### **Image Signal Processing**

Support 16-bit ISP AE/AF/AWB Backlight compensation Chromatic aberration correction Color correction Defective pixel concealment Defog De-mosaic with anti-aliasing filter Edge enhancement **Electronic Image Stabilization** False color suppression Fish-eye lens correction Flicker detection Gamma correction Lens distortion correction Lens shading correction Perspective correction Temporal and spatial noise reduction Wide dynamic range

# Video capability

1280x720 @ 120fps 1920x1080 @ 60fps 5MP @ 25fps 16MP @ 7fps

#### MCU

Built-in 8051 micro controller Support external serial flash for program code Support EEPROM for setting and code

#### Other Functions

Hardware motion detection Privacy zone OSD Support Auto-focus Support Optical Zoom function Support Iris control DDR3 SPI (for Flash Memory) GPIO / PWM / UART / I2C

### Package Information

| Marking   | VC7103BTNA  |

|-----------|-------------|

| Package   | BGA-421pins |

| Dimension | 15x15mm     |

# HD Camera Image Signal Processor

VC7103

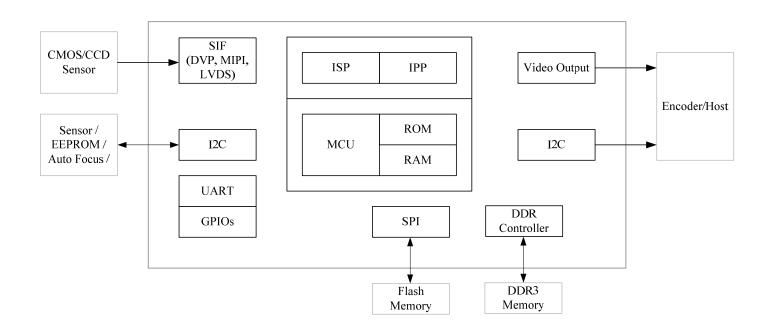

## **Chip Block Diagram**